# Dual-Layer Dielectric Stack for Thermally Isolated Low-Energy Phase-Change Memory

Scott W. Fong<sup>®</sup>, Christopher M. Neumann, Eilam Yalon<sup>®</sup>, Miguel Muñoz Rojo<sup>®</sup>, Eric Pop, *Senior Member, IEEE*, and H.-S. Philip Wong, *Fellow, IEEE*

Abstract—High reset energy is an ongoing issue for phase-change memory (PCM) devices. Prior work demonstrates that smaller PCM switching volume and thermal isolation can reduce the reset energy. In this paper, we fabricate and measure a planar confined PCM device with a multilayer dual-layer stack (DLS) of  $\rm SiO_2/Al_2O_3$  insulator. Devices with contact area of  $\rm 500 \times 20$  nm and lengths of 2  $\mu m$  show exceptionally low reset energies of 18.25  $\pm$  15.8 pJ and low reset current densities of 0.94  $\pm$  0.51 MA/cm². Implementing the DLS enables a 60% reduction in reset energy compared with SiO<sub>2</sub>-isolated devices.

*Index Terms*— Phase-change memory (PCM), reset energy, thermal conductivity, thermal design.

#### I. INTRODUCTION

HASE-CHANGE memory (PCM) has reached production as a nonvolatile storage-class memory (SCM), with access times and costs between NAND flash and DRAM [1]-[3]. In order to create high-density SCM, lower reset energy PCM is required. The high reset energy stems from the temperatures (between 800-1000 K) required to heat and melt the phase-change layer [1]. Two main techniques have been implemented toward lowering the reset energy: reducing the phase-change volume melted via device size scaling [4]–[8] and cell design [9]-[12] or achieving better heat confinement in the structure to create higher temperatures for an applied energy [13]-[15]. To reduce the volume melted, small contact areas have been implemented, down to two nm via carbon nanotube contacts, lowering the reset energy to  $\sim 1$  pJ [5]–[7]. In addition, unique cell designs, such as mushroom [8], edge [9], [10], and confined [11] structures have been implemented to limit the phase-change volume melted. Several works investigated the thermal confinement of the mushroom type structure by implementing thermally resistive

Manuscript received June 26, 2017; revised August 25, 2017; accepted September 20, 2017. Date of current version October 20, 2017. This work was supported by the member companies of the Stanford Non-Volatile Memory Technology Research Initiative, Stanford University. The work of S. W. Fong was supported by the National Science Foundation Graduate Research Fellowship under Grant DGE-4747. The review of this paper was arranged by Editor G. Koh. (Corresponding author: Scott W. Fong.)

The authors are with the Department of Electrical Engineering and Stanford SystemX Alliance, Stanford University, Stanford, CA 94305 USA (e-mail: swfong@stanford.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2756071

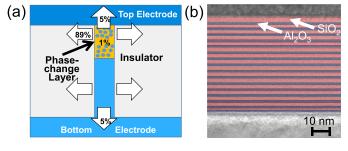

Fig. 1. (a) Schematic of confined cell device structure used for low-power PCM [11]. Arrows represent heat loss paths and energy stored in the phase-change layer during heating. Adapted from [16]. (b) False-colored TEM of the  $\mathrm{SiO_2/Al_2O_3}$  multilayer insulator. This film exhibits lower thermal conductivity compared with  $\mathrm{SiO_2}$  [16]. This paper implements the multilayer insulator into a planar confined cell to reduce insulator heat loss.

bottom electrodes. TiN/TaN multilayers [13], fullerenes [14], and graphene bottom electrodes [15] were used and show 90% power reduction, 75% current reduction, and 40% current reduction compared with control devices with standard electrodes, respectively. For confined and edge structures, the relative heat loss through the surrounding insulators is significantly higher. Specifically, for confined cells as shown in Fig. 1(a), thermal simulations show that 89% of the heat is dissipated into the insulator [16]. A strong reduction of the reset energy is predicted by reducing the thermal conductivity of the insulator [16], [17].

In this paper, we implement an SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> multilayer [16], [17] for the insulator of a planar confined PCM device. A false-colored TEM of the multilayer SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dual-layer stack (DLS) is shown in Fig. 1(b). Devices using the DLS as the insulator require  $\sim 60\%$  less reset energy than devices with SiO<sub>2</sub>. Scanning thermal microscopy (SThM) and Raman mapping are used to identify the highest temperature region and thus the phase-transformation region: the interface between the phase-change layer and the patterned electrode. Scaling the phase-change volume (via length scaling) reduces the energy, implying that the bulk region is where most of the energy is generated during switching. The fabrication process flow and a further description of the multilayer SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> are described in Section II. Section III describes how the various device electrical measurements were conducted. Specifically, the following data will be presented: DC sweep response,

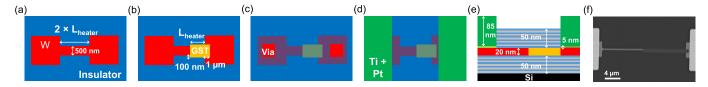

Fig. 2. (a)–(d) Process flow to fabricate planar confined PCM devices (top view). (a) First, an insulator blanket layer of either SiO<sub>2</sub> or DLS was deposited. Then, W was e-beam evaporated. The W was then patterned to form pads and lines, while the remaining area was dry-etched. (b) Phase-change region was patterned, then W was dry-etched, and then a GST layer was deposited and lifted-off. This created a self-aligned GST region. (c) Top insulator blanket layer was deposited with the same film as the bottom layer. The insulator layer was then patterned and wet-etched to form vias to contact the pads. (d) Large pads were then patterned. Ti + Pt was deposited to form the pads and contact the PCM device. (e) Side profile view of the final fabricated structure. (f) SEM of the final fabricated device (top view).

resistance transition due to applied current, endurance, and reset energy for different device dimensions. In Section IV, SThM measurements will be used to identify the location of the switching region and finite-element (FE) simulations and analytical models will be used to describe the heat generation through the PCM device.

## II. FABRICATION PROCESS FLOW AND DIELECTRIC STACK

The planar confined PCM devices were fabricated using the process flow outlined in Fig. 2. First, the bottom insulator layer was deposited onto Si wafers. The samples were split between control films, which had 50 nm of plasmaenhanced chemical vapor deposition (PECVD) SiO2, and DLS films, which had an atomic layer deposition (ALD) oxide comprising of [SiO<sub>2</sub> (2)/Al<sub>2</sub>O<sub>3</sub> (1)]<sub>17</sub> multilayer (where [SiO<sub>2</sub> (A)/Al<sub>2</sub>O<sub>3</sub> (B)]<sub>C</sub> means A-nm thick SiO<sub>2</sub> layers and B-nm thick Al<sub>2</sub>O<sub>3</sub> layers repeated C times). The ALD SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> were deposited using O<sub>2</sub> plasma with Tris[dimethylamino]silane for SiO<sub>2</sub> and Trimethylaluminum for Al<sub>2</sub>O<sub>3</sub> deposition. Next, a 20-nm W layer was deposited using e-beam evaporation. The W layer was then patterned and dry-etched with SF<sub>6</sub> [20] to form the electrode pads and metal line. For the W line, the width remaining was 500 nm and the length was varied to 4, 10, and 20 µm. Next, half of the metal region was patterned to form the phase-change region. The width for this pattern was 500 + 100 nm overshoot on each edge (to account for misalignment to the W metal line) and the length was half of the W line length  $+1 \mu m$  into the pad. This patterned region was then etched to remove all of the W and filled with 20 nm of sputtered Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST). The remaining GST on the unpatterned regions was then lifted off to create the self-aligned phase-change layer seen in Fig. 2(b). Following lift-off, the entire wafer was coated with a top insulator. The SiO<sub>2</sub> control samples were formed by depositing 10 nm of ALD SiO<sub>2</sub> + 40 nm of PECVD SiO<sub>2</sub>. The DLS samples were formed by ALD depositing [SiO<sub>2</sub> (2)/Al<sub>2</sub>O<sub>3</sub> (1)]<sub>17</sub>. After the top insulator was deposited, via holes were patterned and wet-etched with 20:1 buffered oxide etch to contact the metal pads. Finally, 5-nm Ti + 85-nm Pt pads were patterned, deposited by e-beam evaporation, and lifted off. The final structure is shown via scanning electron microscope (SEM) in Fig. 2(f).

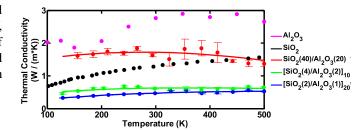

The multilayer DLS film comprising of [SiO<sub>2</sub> (2)/Al<sub>2</sub>O<sub>3</sub> (1)] repeated shows low thermal conductivity and was developed

Fig. 3. Through-plane thermal conductivity of  $SiO_2/Al_2O_3$  multilayers with 60-nm total thickness and varying individual layer thicknesses ([SiO\_2 (A)/Al\_2O\_3 (B)]\_C means A-nm thick SiO\_2 layers and B-nm thick  $Al_2O_3$  layers repeated C times). The thermal conductivity decreases as the layer thickness decreases [16]. The multilayer films exhibit lower thermal conductivity than their bulk ALD SiO\_2 [18] and  $Al_2O_3$  [19] constituents

in previous work [16]. The through-plane thermal conductivity of this film was measured using a steady-state electrothermal measurement of a metal heater on the film [16]. By measuring the change in electrical resistance of the metal heater due to applied power and at different temperatures, the thermal resistance of the multilayer film was extracted [16], [21]. Then, assuming 1-D heat conduction through the film, an effective thermal conductivity was calculated. Samples with various number of layers with the same total thickness (60 nm) were deposited, and the resulting thermal conductivities are shown in Fig. 3. The thermal conductivity of the DLS film is significantly lower than bulk ALD SiO<sub>2</sub> [18] and Al<sub>2</sub>O<sub>3</sub> [19] films. Increasing the number of layers reduces the thermal conductivity, ultimately reaching a 64% reduction when compared with the bulk SiO<sub>2</sub> thermal conductivity. The decrease in thermal conductivity is attributed to two main reasons: a change in film quality resulting in lower density and thus lower intrinsic thermal conductivity of each of the layers, and a finite thermal boundary resistance (TBR) between the two layers of  $\sim 1.5 \text{ m}^2\text{K/GW}$ , which contributes significantly when the number of layers is large [16]. This multilayer film was leveraged to create a thermally confined PCM device [17] and is further explored in this paper.

#### III. ELECTRICAL MEASUREMENTS

Electrical resistance measurements of the devices were performed using an HP 4156C Parameter Analyzer, programming pulses were applied via an Agilent 811110A pulse generator, and a 707B Keithley switch matrix was used

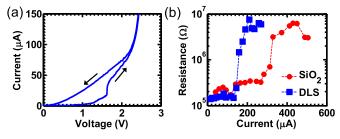

Fig. 4. For a typical  $L_{\rm heater}=10~\mu{\rm m}$  device. (a) I-V curve obtained from a DC voltage sweep of a SiO<sub>2</sub>-insulated device. The device starts in the reset (high resistance) state and undergoes threshold switching. The device's resistance is then set to the low resistance state as the DC sweep returns. (b) R-I plot of the SiO<sub>2</sub> and DLS-insulated device's response to reset pulses with various voltages. The voltages applied are increased in 0.5-V steps. The resulting current increases, resulting in larger energies generated in the PCM device. The devices switch to the reset state once a large enough energy is applied. The SiO<sub>2</sub> devices switch with 341  $\pm$  27  $\mu{\rm A}$ , while the DLS devices switch with 190  $\pm$  13  $\mu{\rm A}$  (25 measurements on the same device).

to switch between the two tools. A 200-mV DC voltage was used to read the resistance of the device. Reset and Set were performed by applying a 5/50/5 and 100/1000/100 ns rise/width/fall time pulse, respectively. During programming, the input impedance of a Tektronix DPO4045 Oscilliscope was used as a  $50-\Omega$  resistor to ground to measure the current. For all of the following measurements, the devices were first cycled  $\sim 1000$  times before the actual measurements to prevent any anomalous effects associated with early cycle switching, such as phase-segregation [22].

Several electrical measurements were performed, including a DC voltage sweep to set the devices, an R–I curve showing the resistance and currents measured after applying different voltages, from which the average reset energy was derived. First, the DC sweep was measured to identify the threshold switching voltage. Fig. 4(a) shows an example of the DC sweep performed on the  $L_{\rm heater}=10~\mu{\rm m}$ . The devices showed a threshold voltage between 1 and 2 V. Next, pulsed measurements were performed via gradually increasing voltages, with 0.5 or 0.2 V steps for reset and set. As the voltage pulses were applied, the current during each pulse,  $I_{\rm reset}$ , was determined using the following equation:

$$I_{\text{reset}} = \frac{1}{t_{\text{pulse}}} \int \frac{V_{\text{osc}}(t)}{50\Omega} dt \tag{1}$$

where  $V_{\rm osc}(t)$  was the measured voltage across the 50- $\Omega$  oscilloscope resistor as a function of time and  $t_{\rm pulse}$  is the total time the pulse was applied at its maximum value. For the 5/50/5 ns rise/width/fall time pulse, 55 ns was used since 1/2 × [5-ns rise + 5-ns fall] + 50 ns pulsewidth = 55 ns. Fig. 4(b) shows an example of the resulting currents and DC resistance after pulses were applied on the  $L_{\rm heater}=10~\mu{\rm m}$  devices. The devices were initially in the set state ( $R_{\rm set} \leq 200~{\rm k}\Omega$ ) and switch to the reset state ( $R_{\rm reset} \geq 2~{\rm M}\Omega$ ) after undergoing the voltage pulses. The  $L_{\rm heater}=2$ , 5, 10  $\mu{\rm m}$  DLS devices switch at 94  $\pm$  51, 129  $\pm$  62, and 190  $\pm$  13  $\mu{\rm A}$ , while the SiO<sub>2</sub> devices switch at 240  $\pm$  83, 329  $\pm$  70, 341  $\pm$  27  $\mu{\rm A}$ , respectively (25 measurements on a single devices for each length). The  $L_{\rm heater}=2~\mu{\rm m}$  DLS devices were thus able to show current densities of 0.94  $\pm$  0.51 MA/cm<sup>2</sup>.

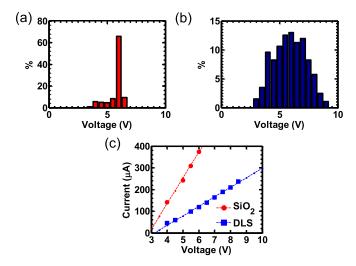

Fig. 5. For a typical  $L_{\rm heater}=5~\mu{\rm m}$  device. (a)and (b) Histogram distribution of the voltages required to reset the (a) SiO<sub>2</sub> and (b) DLS device. Steps of 0.5 V were taken using the write-verify process until the device showed resistance  $> R_{\rm reset}$ . (c) Plot of the measured currents to reset a device at their associated reset voltages. 25 measurements each were taken for DLS and SiO<sub>2</sub> devices. The current variation at a given reset voltage was  $<\pm5\%$ .

A write-verify process was used to cycle the devices and identify the reset energy. In order to perform the process, a 2-V reset pulse is first applied. After the reset pulse, the device resistance is measured. If the resistance measured is below the  $R_{\text{reset}}$  threshold, then another reset pulse is applied, increasing the previous voltage by 0.5-V increments. The reset pulses are increase until the resistance is above the  $R_{reset}$ threshold. Then, set pulses are applied in a similar manner with 0.8-V starting set voltage and 0.2-V steps until the resistance measured is below the  $R_{\text{set}}$  threshold. The process was repeated to cycle the device. Fig. 5(a) and (b) shows the required voltage measured to reset  $L_{\text{heater}} = 5 \, \mu \text{m SiO}_2$ and DLS devices. The current driven at reset was measured 25 times randomly selected from 1000 cycles for each of the device dimensions. An example plot of the measured currents and voltages during reset for the  $L_{\text{heater}} = 5 \, \mu \text{m}$  DLS and SiO<sub>2</sub> devices is shown in Fig. 5(c). There is a strong linear correlation between the reset voltage,  $V_{\text{reset}}$ , and current,  $I_{\text{reset}}$ . Thus, the reset current can be written as a function of the reset voltage,  $I_{reset}(V_{reset})$ . In addition, for a given reset voltage, the current driven does not change significantly between cycles. The variation in reset current is mostly due to the variation in the required voltage to reset. The energy required to reset PCM devices can thus be estimating using

$$E_{\text{reset}} = V_{\text{reset}} \times I_{\text{reset}}(V_{\text{reset}}) \times t_{\text{pulse}}.$$

(2)

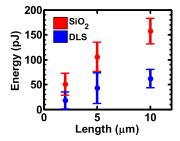

The reset energy was measured for DLS and SiO<sub>2</sub> samples with  $L_{\rm heater}=2,5$ , and 10 µm and is shown in Fig. 6. The DLS devices require  $\sim 60\%$  lower energies to switch compared with the SiO<sub>2</sub>-isolated devices at all dimensions. In addition, the reset energy decreases with the overall length of the device with the  $L_{\rm heater}=2$  µm devices showing  $18.25\pm15.8$  pJ switching energies. The devices were also cycled for endurance testing using the write-verify process.

Fig. 6. Energy required to reset devices with different  $L_{\text{heater}}$  length for SiO<sub>2</sub> and DLS devices. The energy was determined using (2). The DLS devices required  $\sim$ 60% less energy to reset than the SiO $_2$  devices at all lengths. Decreasing the length shows a decrease in reset energy which implies that most of the reset energy is consumed in the bulk volume of the phase-change layer and not at the interface.

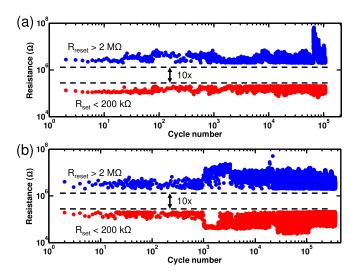

Fig. 7. Measured endurance of  $L_{\text{heater}} = 10 \ \mu\text{m}$  (a) SiO<sub>2</sub> and (b) DLS PCM devices. A write-verify process was used. Devices with all different  $L_{\text{heater}}$  dimensions were able to maintain  $10 \times$  resistance window for  $> 10^5$  cycles.

Devices for all dimensions showed  $> 10^5$  endurance cycles. Fig. 7 shows the endurances measured for the SiO<sub>2</sub> and DLS  $L_{\text{heater}} = 10 \ \mu\text{m}$  devices.

### IV. STHM MEASUREMENTS, FE SIMULATIONS, AND ANALYSIS

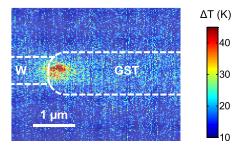

To better understand the power dissipation in the device, the temperature distribution was measured using SThM [23] and Raman thermometry [24], [25]. A commercial SThM module by Anasys Instruments was added onto an atomic force microscope (AFM) from Veeco Instruments. A Horiba LabRam instrument with a 633-nm laser was used for a Raman thermometry following the procedure outlined in [24]. The SThM enables high (AFM-based) spatial resolution, but measures the temperature at the top surface of the insulator layer. On the other hand, Raman directly measures heating in the GST film, but is limited by diffraction to a spatial resolution of  $\sim 0.5 \mu m$ . The SThM measurement is used to identify the relative temperature profile, while the Raman measurement is used to identify the temperature at the GST layer and hence calibrate the SThM measurement.

SThM image of DLS PCM device ( $W_{\text{heater}} = 1 \ \mu \text{m}$  and  $L_{\text{heater}} = 5 \ \mu\text{m}$ ) showing the temperature rise under electrical bias ( $V=3~{

m V}$  and  $I\approx 200~{

m \mu A}$  DC during SThM surface temperature mapping) [23]. The temperature was calibrated by a Raman thermometry [24]. The GST channel and W electrode boundaries (dashed white lines) are visible in an AFM topography image acquired simultaneously with the SThM map. The temperature profile shows significant heating at the W/GST contact interface and moderate heating in the bulk GST.

Fig. 8 shows the spatial distribution of the temperature rise for a DLS PCM device ( $W_{\text{heater}} = 1 \, \mu \text{m}$  and  $L_{\text{heater}} = 5 \, \mu \text{m}$ ). The AFM topography map acquired simultaneously determines the exact position of the GST channel and the electrodes (marked with white dashed lines). Evidently, the highest temperature region is locally at the W/GST contact with some temperature change also generated throughout the bulk GST channel. This implies that the phase-change switching region is near the interface, since that is the highest temperature region. In addition, the finite temperature change along the bulk GST implies that significant power is consumed along the bulk GST to heat up the entire region. Since the bulk volume is much larger than the interfacial switching region, significant power is required to reach even a small temperature change of the bulk GST.

2-D FE simulations were performed to better understand the heating and improvement from using the DLS film. The following Fourier heat diffusion equations with TBRs were used to simulate the steady-state heat flow:

$$\nabla \cdot (k\nabla T) + Q_{\text{heat}} = 0 \tag{3}$$

$$\nabla \cdot (k\nabla T) + Q_{\text{heat}} = 0 \tag{3}$$

$$Q'' = \frac{\Delta T}{\text{TBR}} \tag{4}$$

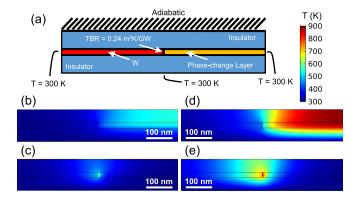

where (3) was solved at each node with the following node parameters: k is the thermal conductivity, T is the temperature, and  $Q_{\text{heat}}$  is the heat generated. For the W/GST interface, Q'' was the heat flux across the interface and had a TBR of 24 m<sup>2</sup>K/GW [26]. Fig. 9(a) outlines all boundary conditions used for the simulation. The W and GST contacts with the pad region and Si wafer were assumed to be isothermal, since they act as a heat sink/reservoir, with volumes much larger than the regions simulated. The thermal conductivities used were identical to previous work [16], except for the insulator. The insulator thermal conductivities were selected to match their high temperature values of 1.6 and 0.48 W/(m  $\times$  K) for SiO<sub>2</sub> and DLS films, respectively [16].

Joule heating was assumed to be the primary heat source for this simulation. Thus, the heat generated could be broken up into two different heating types based on the most electrically resistive locations: 1) the heat generated at the interface to

Fig. 9. 2-D FE thermal simulation. (a) Simulation boundary conditions and temperature legend. (b)–(e) Resulting simulation temperature profiles. Simulations compared (b) and (c)  $SiO_2$  devices and (d) and (e) DLS devices. Devices with different  $L_{\rm heater}$  lengths were simulated, and the normalized temperature profile near the GST/W interface appeared the same, since the heat transfer length is much shorter than the bulk GST and W length. (b) and (d) Simulations assuming all heat generated in the bulk GST. For the same power, that DLS devices generate  $2.4\times$  the temperature change of  $SiO_2$  devices. (c) and (e) Simulations assuming all heat generated at the GST/W interface. For this case, heating of the interface showed  $1.6\times$  the temperature change in DLS devices compared with  $SiO_2$  devices.

simulate the effect of contact resistance and 2) the heat generated in the bulk of the phase-change region. In addition, any potential heating from the contact thermoelectric effect could be lumped with the contact resistance heating. Heating may have also occurred in the bulk W, but the measured resistance of W only lines (identical to devices except without the W etch/ GST deposition step) was significantly lower than the PCM devices. Also, SThM measurements did not show a temperature change in the bulk W region, thus the energy consumed by the W was likely not significant.

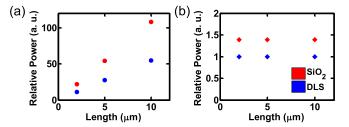

Fig. 9(b) and (d) shows the simulated temperature change due to bulk heating for SiO<sub>2</sub> and DLS films, respectively. In the case of bulk heating, most of the heat is dissipated through the insulator stack and thus, the thermal resistance is inversely related to the insulator thermal conductivity. Since the thermal resistance represents the temperature change generated per applied power, this means that the insulator thermal conductivity linearly decreases the energy required to switch. The simulations are in agreement with the analytical estimation, showing a 59% reduction in power to reach the melting temperature for DLS devices compared with the SiO<sub>2</sub> devices. This is in good agreement with the measured energy reduction attained between the SiO<sub>2</sub> and DLS devices. Another important detail to note is the decrease in total power required to reach the melting temperature with  $L_{\text{heater}}$ length. Fig. 10(a) shows the relative power required to reach the melting temperature in the bulk for various dimensions. Since the volume heated decreases linearly with  $L_{\text{heater}}$  length, the required power linearly decreases as well. For interface heating, Fig. 9(c) and (e) show the simulated temperature change due to interface heating for SiO<sub>2</sub> and DLS films, respectively. For this case, the heat travels along the GST and W layers while gradually dissipating into the insulator, similar to a thermal fin. A thermal healing length  $L_{\text{thermal}}$  can

Fig. 10. Simulated reset power required to reach a temperature of 900 K for the different  $L_{\rm heater}$  length PCM devices assuming (a) bulk heating and (b) interface heating. The power was normalized to the power required to reach 900 K for DLS PCM devices assuming interface heating. For bulk heating, the power required decreases with length, since less volume is heated. For interface heating, the power required does not change with length because the heat transfer length is much smaller than  $L_{\rm heater}$ . Using the DLS shows a 59% and 36% reduction in reset power required compared with devices using SiO<sub>2</sub> as the insulator for bulk and interface heating, respectively.

be calculated which is the transfer length of the temperature profile and describes the relationship between the thermal conductivity of the insulator,  $k_{\text{insulator}}$ , and the metal,  $k_W$ , as follows:

$$L_{\rm thermal} \propto \sqrt{\frac{k_W}{k_{\rm insulator}}}.$$

(5)

Thus, the effective volume heated is larger if the insulator thermal conductivity decreases. As a result, the simulated reduction in power is 36% for DLS devices compared with SiO<sub>2</sub> devices. The temperature profile near the GST/W interface was identical for  $L_{\rm heater}=2$ , 5, and 10 µm devices, since the thermal length was  $\sim$ 100 nm, thus  $L_{\rm thermal}\ll L_{\rm heater}$ . In addition, since the volume heated remains constant with device length, the relative power did not depend on  $L_{\rm heater}$  as shown in Fig. 10(b). Simulating only interface heating does not agree with the measured results for both reduction in power from changing the insulator and changing  $L_{\rm heater}$ . Thus, the required energy to switch is consumed mostly with heating up the bulk, rather than heating the switching region at the interface.

The relative energy generated in the two locations can be approximated by assuming that the current is the same for both the bulk GST and the interface region. Thus

$$E_{\text{interface}}/E_{\text{bulk}} = R_{\text{interface}}(T_{\text{interface}})/R_{\text{bulk}}(T_{\text{bulk}})$$

(6)

where  $E_x$  is the energy at location x and  $R_x(T_x)$  is the electrical resistance at temperature T and location x. For the bulk GST region, the resistance decreases over five orders of magnitude as the temperature increases [1]. Thus, the bulk GST region likely consumes a large part of the energy, despite not being the switching region. The interface resistance, however, is less dependent on temperature [27]. Thus, as the bulk heats up and becomes more conductive, gradually more energy is generated at the interface. Therefore, the highest temperature and switching occur at the interface.

The energy required to switch the PCM device can be used as an upper bound for the volume switched. If there is no energy lost to the surroundings, the energy to heat the phasechange layer to the melting temperature and the latent heat of melting is  $\sim 1.2$  aJ/nm³ [28]. For 18 pJ, the energy required to switch the DLS  $L_{\rm heater} = 2~\mu \rm m$  device, the volume melted must be below  $1.5 \times 10^7~\rm nm^3$  or melted length  $< 1.5~\mu \rm m$  for the devices used in this paper. Thus, it is impossible for the entire bulk GST region to be melted and the GST must be switching at the interface. The devices in this paper show much lower energy and reset current density than other reported devices of similar dimensions (typically  $\sim 10~\rm nJ$  and  $\sim 10~\rm MA/cm^2$ ) [4], [17]. Further thermal confinement in the insulators can reduce the reset energy and will continue to show significant benefit for all device structures, including confined cells where the primary heat loss path is into the insulator [16].

#### V. CONCLUSION

This paper utilized the planar confined PCM device to reduce the volume melted, and a thermally resistive multilayer insulator SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> to achieve low reset energy in PCM devices. Reset energies as low as  $18.25 \pm 15.8$  pJ and current densities of  $0.94 \pm 0.51 \text{ MA/cm}^2$  were measured for a contact area of  $A = 10^4$  nm<sup>2</sup> and heater/GST length of  $L_{\text{heater}} = 2 \text{ }\mu\text{m}$ . SThM and Raman mapping suggest that the phase-change region near the heater/GST interface exhibits the highest temperature change and thus represents the switching region. Simulations and analytical models show that most of the energy is used to heat the bulk GST region until the heater/GST contact resistance begins to dominate, at which point the heating and thus switching occurs near the interface. The thermally resistive DLS devices show a strong 60% reset energy reduction and a path to further reduce reset energy via thermal confinement in the insulator.

#### REFERENCES

- [1] H.-S. P. Wong *et al.*, "Phase change memory," *Proc. IEEE*, vol. 98, no. 12, pp. 2201–2227, Dec. 2010.

- [2] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "Overview of candidate device technologies for storageclass memory," *IBM J. Res. Develop.*, vol. 52, nos. 4–5, pp. 449–464, 2008.

- [3] G. W. Burr et al., "Recent progress in phase-change memory technology," IEEE J. Emer. Sel. Topics Circuits Syst., vol. 6, no. 2, pp. 146–162, Jun. 2016

- [4] H.-S. P. Wong et al. (2017). Stanford Memory Trends. [Online]. Available: https://nano.stanford.edu/stanford-memory-trends

- [5] J. Liang, R. G. D. Jeyasingh, H.-Y. Chen, and H.-S. P. Wong, "An ultra-low reset current cross-point phase change memory with carbon nanotube electrodes," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 1155–1163, Apr. 2012.

- [6] F. Xiong, A. D. Liao, D. Estrada, and E. Pop, "Low-power switching of phase-change materials with carbon nanotube electrodes," *Science*, vol. 332, no. 6029, pp. 568–570, 2011.

- [7] F. Xiong et al., "Self-aligned nanotube—Nanowire phase change memory," Nano Lett., vol. 13, no. 2, pp. 464–469, 2013.

- [8] A. Pirovano, A. L. Lacaita, A. Benvenuti, F. Pellizzer, S. Hudgens, and R. Bez, "Scaling analysis of phase-change memory technology," in *IEDM Tech. Dig.*, Dec. 2003, pp. 29.6.1–29.6.4.

- [9] Y. H. Ha et al., "An edge contact type cell for phase change RAM featuring very low power consumption," in *Proc. VLSIT*, Jun. 2003, pp. 175–176.

- [10] A. Pirovano et al., "Self-aligned μTrench phase-change memory cell architecture for 90 nm technology and beyond," in Proc. ESSDERC, Sep. 2007, pp. 222–225.

- [11] D. H. Im *et al.*, "A unified 7.5 nm dash-type confined cell for high performance PRAM device," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [12] Y. Sasago et al., "Phase-change memory driven by poly-Si MOS transistor with low cost and high-programming gigabyte-per-second throughput," in Proc. VLSIT, Jun. 2011, pp. 96–97.

- [13] J.-Y. Wu et al., "A low power phase change memory using thermally confined TaN/TiN bottom electrode," in *IEDM Tech. Dig.*, Dec. 2011, pp. 3.2.1–3.2.4.

- [14] C. Kim et al., "Fullerene thermal insulation for phase change memory," Appl. Phys. Lett., vol. 92, no. 1, p. 013109, 2008.

- [15] C. Ahn et al., "Energy-efficient phase-change memory with graphene as a thermal barrier," Nano Lett., vol. 15, no. 10, pp. 6809–6814, 2015.

- [16] S. W. Fong et al., "Thermal conductivity measurement of amorphous dielectric multilayers for phase-change memory power reduction," J. Appl. Phys., vol. 120, no. 1, p. 015103, 2016.

- [17] S. W. Fong, C. M. Neumann, and H.-S. P. Wong, "Dual-layer dielectric stack for thermally-isolated low-power phase-change memory," in *Proc. Int. Memory Workshop*, May 2017, pp. 1–4.

- [18] D. G. Cahill, "Thermal conductivity measurement from 30 to 750 K: The 3ω method," Rev. Sci. Instrum., vol. 61, no. 2, pp. 802–808, 1990.

- [19] A. Cappella et al., "High temperature thermal conductivity of amorphous Al<sub>2</sub>O<sub>3</sub> thin films grown by low temperature ALD," Adv. Eng. Mater., vol. 15, no. 11, pp. 1046–1050, 2013.

- [20] G. Larrieu and E. Dubois, "Reactive ion etching of a 20 nanometers tungsten gate using a SF<sub>6</sub>/N<sub>2</sub> chemistry and hydrogen silsesquioxane hard mask resist," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 23, no. 5, pp. 2046–2050, 2005.

- [21] Y. C. Tai, C. H. Mastrangelo, and R. S. Müller, "Thermal conductivity of heavily doped low-pressure chemical vapor deposited polycrystalline silicon films," *J. Appl. Phys.*, vol. 63, no. 5, p. 1442, 1988.

- [22] W. Kim et al., "ALD-based confined PCM with a metallic liner toward unlimited endurance," in *IEDM Tech. Dig.*, Dec. 2016, pp. 4.2.1–4.2.4.

- [23] T. Borca-Tasciuc, "Scanning probe methods for thermal and thermoelectric property measurements," *Annu. Rev. Heat Transf.*, vol. 16, no. 16, pp. 211–258, 2013.

- [24] E. Yalon et al. (Jun. 2017). "Spatially resolved thermometry of resistive memory devices." [Online]. Available: https://arxiv.org/abs/1706.02318

- [25] E. Yalon et al., "Energy dissipation in monolayer MoS<sub>2</sub> electronics," Nano Lett., vol. 17, no. 6, pp. 3429–3433, 2017.

- [26] J. Lee, E. Bozorg-Grayeli, S. Kim, M. Asheghi, H.-S. P. Wong, and K. E. Goodson, "Phonon and electron transport through Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> films and interfaces bounded by metals," *Appl. Phys. Lett.*, vol. 102, no. 19, p. 191911, 2013.

- [27] D. Roy, M. A. A. in't Zandt, and R. A. M. Wolters, "Specific contact resistance of phase change materials to metal electrodes," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1293–1295, Nov. 2010.

- [28] F. Xiong et al., "Towards ultimate scaling limits of phase-change memory," in *IEDM Tech. Dig.*, Dec. 2016, pp. 4.1.1–4.1.4.

Scott W. Fong received the B.S. degree in engineering physics from the University of Illinois at Urbana–Champaign, Champaign, IL, USA, and the M.S. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2013, where he is currently pursuing the Ph.D. degree, with a focus on phase-change memory device simulation and fabrication to improve performance via thermal design.

Christopher M. Neumann received the B.S. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign, Champaign, IL, USA, in 2012 and the M.S. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2015, where he is currently pursuing the Ph.D. degree. His research interests include 2-D materials and resistive switching and phase change memory devices.

**Eilam Yalon** received the B.S. degree in materials engineering and physics and the Ph.D. degree in electrical engineering from the Technion–Israel Institute of Technology, Haifa, Israel, in 2009 and 2015, respectively.

He is currently a Post-Doctoral Researcher with Stanford University, Stanford, CA, USA with a focus on energy efficient memory and computing devices via 2-D, resistive switching, and phase-change materials.

**Eric Pop** (M'99–SM'11) received the B.S. and M.S. degrees from the Massachusetts Institute of Technology, Cambridge, MA, USA, and the Ph.D. degree from Stanford University, Stanford, CA, USA.

He is currently an Associate Professor of electrical engineering with Stanford University. His current research interests include energy efficient electronics and data storage, novel 2-D and 1-D devices & materials, and energy conversion and harvesting.

Miguel Muñoz Rojo received the Ph.D. degree in condensed matter physics & nanotechnology and the M.S./B.S. degree in physics from the Autonomous University of Madrid.

He is currently a Post-Doctoral Researcher with Stanford University, Stanford, CA, USA. His current research focus is the transport properties of novel 2-D materials and their applications in electrical and thermal devices.

H.-S. Philip Wong (F'01) was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, from 1988 to 2004. He joined Stanford University, Stanford, CA, USA, as a Professor of electrical engineering, in 2004, where he is currently the Willard R. and Inez Kerr Bell Professor. He is the founding Faculty Co-Director of the Stanford SystemX Alliance, an industrial affiliate program focused on building systems.