## Localized Heating in MoTe<sub>2</sub>-Based Resistive Memory Devices

Isha M. Datye, Miguel Muñoz Rojo, Eilam Yalon, Michal J. Mleczko, and Eric Pop\* *Electrical Engineering, Stanford University, Stanford, CA 94305, USA \*E-mail: epop@stanford.edu*

Layered materials like transition metal dichalcogenides (TMDs) and hexagonal boron nitride (h-BN) have been recently demonstrated as the switching layers in resistive random access memory (RRAM) devices [1-3], but their switching mechanisms are not yet well understood. In this work, we show resistive memory switching in MoTe<sub>2</sub> devices and investigate the thermal origins of their switching behavior using scanning thermal microscopy (SThM). We observe localized heating due to the formation of a conductive plug, which is correlated with electro-thermal simulations, providing the first thermal insights into the operation of such RRAM devices.

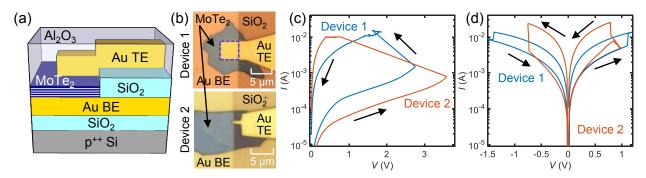

We fabricated vertical MoTe<sub>2</sub> devices (**Fig. 1a-b**) using mechanically exfoliated MoTe<sub>2</sub> crystals grown by chemical vapor transport (CVT). Thin MoTe<sub>2</sub> was transferred onto Ti/Au (5/40 nm) bottom electrodes (BE) patterned by electron beam (e-beam) lithography and deposited by e-beam evaporation. We patterned and e-beam evaporated SiO<sub>2</sub> (65 nm thick) onto part of the MoTe<sub>2</sub> to isolate the Au bottom and top electrodes (TE). The Au TEs (80 nm thick) were then patterned and evaporated onto the MoTe<sub>2</sub>, and the devices were capped with ~10 nm Al<sub>2</sub>O<sub>3</sub> by atomic layer deposition (ALD) [4]. We performed all exfoliation, transfer, metal lift-off, and ALD steps in a N<sub>2</sub> glove box with <3 ppm O<sub>2</sub> and H<sub>2</sub>O, to prevent degradation of the MoTe<sub>2</sub>.

Fig. 1c displays current-voltage (*I-V*) measurements of forming in two devices (Devices 1 and 2). A series resistor was used to limit the current through the device during forming. After the initial forming step the devices show bipolar switching between low and high resistive states (LRS and HRS), as shown in Fig. 1d, which is representative of  $\sim$ 20 vertical MoTe<sub>2</sub> devices we measured.

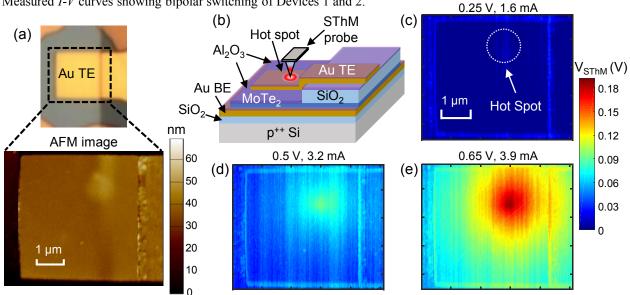

Scanning thermal microscopy (SThM) measurements were performed on the surface of Device 1 in the LRS after the forming step. SThM is an atomic force microscope (AFM) based technique that uses a thermally resistive probe to obtain heating maps of a device under bias with nanoscale resolution [5]. Fig. 2a shows optical and AFM topographic images of the TE region (capped with Al<sub>2</sub>O<sub>3</sub>). Fig. 2b shows a schematic of the SThM setup on the device geometry. Figs. 2c-e display SThM images taken at 0.25 V, 0.5 V, and 0.65 V between the TE (applied voltage) and BE (ground). The colorbar shows the output SThM voltage, which is proportional to the temperature rise  $\Delta T$ . At low voltage (0.25 V), a hot spot appears (see Fig. 2c). At higher voltages (0.5 V and 0.65 V) the hot spot grows larger and is clearly observed on the Au TE, revealing localized heating in the device (see Figs. 2d-e). This localized heating suggests the formation of a conductive plug. Importantly, these SThM measurements provide direct evidence that the switching mechanism is a thermally-activated process such as localized phase change [2], defect (i.e. vacancy) generation, or Te migration in the MoTe<sub>2</sub> [6].

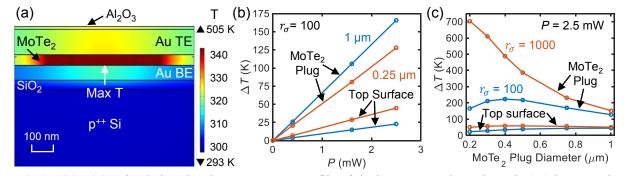

Next, we used three-dimensional (3D) simulations to estimate the device  $\Delta T$  during operation, as the (surface) SThM does not give a direct measurement of the (buried) plug. We considered lower and upper bounds of 100 and 1000 (based on the resistance change in the devices) for the ratio ( $r_{\sigma}$ ) between the electrical conductivity in the MoTe<sub>2</sub> plug and the film. **Fig. 3a** shows a temperature profile of a cross-section of the device for a conductive plug diameter of 300 nm and  $r_{\sigma} = 100$ . As expected, the hottest part of the device is the conductive plug, while the top and bottom surfaces are much cooler due to heat dissipation in the electrodes and in the substrate. **Fig. 3b** shows the simulated  $\Delta T$  of the device vs. power for two plug diameters (0.25 and 1  $\mu$ m) and  $r_{\sigma} = 100$ . **Fig. 3c** shows simulated  $\Delta T$  of the conductive plug and the top surface of the device vs. plug diameter at different power inputs and  $r_{\sigma}$ . From a preliminary analysis, we estimate that the peak  $\Delta T$  of the top surface of the device with a power input of 2.5 mW, i.e. similar to our experimental conditions, ranges from ~23 to 60 K, depending on the conductive plug diameter and  $r_{\sigma}$ . We note that the corresponding plug temperature is more sensitive to diameter than the surface temperature, resulting in a larger plug temperature range (see Fig. 3c).

In summary, we observed localized heating in MoTe<sub>2</sub>-based memory devices for the first time, pointing to the temperature-activated switching mechanism. This work was supported in part by the NSF-EFRI 2-DARE program, the Stanford NMTRI, and a NDSEG fellowship (I.M.D.). We acknowledge assistance with MoTe<sub>2</sub> growth from Ian Fisher and Hsueh-Hui Kuo.

**Refs:** [1] R. Ge, *et al.*, *Nano. Lett.* **18**, 434 (2018). [2] F. Zhang, *et al.*, arXiv: 1709.03835 (2017). [3] Y. Shi, *et al.*, *IEDM* (2017). [4] M.J. Mleczko, *et al.*, *ACS Nano* **10**, 7507 (2016). [5] D.G. Cahill, *et al.*, *J. Appl. Phys.* **93**, 793 (2003). [6] S. Yoo, *et al.*, *Nanoscale* **7**, 6340 (2015).

**Fig. 1:** (a) Schematic of vertical MoTe<sub>2</sub> memory devices with Au top and bottom electrodes (TE and BE, respectively) and SiO<sub>2</sub> isolation layers. (b) Top view optical images of two devices, Device 1 (~30 nm thick MoTe<sub>2</sub>) and Device 2 (~55 nm MoTe<sub>2</sub>), with top electrode areas of  $4.5 \times 4.5 \ \mu\text{m}^2$  (dashed outline) and  $0.7 \times 0.4 \ \mu\text{m}^2$ , respectively. (c) Measured *I-V* curves showing forming of Devices 1 and 2, with arrows corresponding to the direction of the voltage sweeps. For all measurements, the voltage is applied to the TE, and the BE is grounded. (d) Measured *I-V* curves showing bipolar switching of Devices 1 and 2.

**Fig. 2:** (a) Optical and AFM images of Device 1 showing the TE region. (b) Schematic of SThM setup showing the probe on the sample surface. SThM images of Device 1 (after forming, in the LRS) at (c) 0.25 V, (d) 0.5 V, and (e) 0.65 V. The colorbar corresponds to the output SThM voltage, which is proportional to temperature rise  $\Delta T$ . A hot spot (corresponding to the bump on the TE seen in the AFM) is observed as the applied voltage increases, showing evidence of localized heating due to a conductive plug in the device.

Fig. 3: (a) COMSOL simulation showing temperature profile of device cross-section. The ratio  $(r_{\sigma})$  between the electrical conductivity in the MoTe<sub>2</sub> film and plug is 100. The simulation was performed at P = 2.5 mW for a MoTe<sub>2</sub> plug diameter of 300 nm, showing a maximum temperature of ~500 K. (b) Simulated top surface  $\Delta T$  vs. P, for two different MoTe<sub>2</sub> plug diameters at  $r_{\sigma} = 100$ . (c) Simulated  $\Delta T$  vs. MoTe<sub>2</sub> plug diameter for P = 2.5 mW at the top surface and inside the MoTe<sub>2</sub> plug for different  $r_{\sigma}$ .